APPLIED PHYSICS LETTERS VOLUME 75, NUMBER 9 30 AUGUST 1999

## Si resonant interband tunnel diodes grown by low-temperature molecular-beam epitaxy

Phillip E. Thompson, a) Karl D. Hobart, Mark E. Twigg, and Glenn G. Jernigan *Naval Research Laboratory, Washington, DC 20375-5347*

Thomas E. Dillon, Sean L. Rommel, and Paul R. Berger

Department of Electrical and Computer Engineering, University of Delaware, Newark, Delaware 19716-3130

David S. Simons and Peter H. Chi

National Institute of Standards and Technology, Gaithersburg, Maryland 20899

Roger Lake and Alan C. Seabaugh

Applied Research Laboratory, Raytheon Systems Company, Dallas, Texas 75243

(Received 20 April 1999; accepted for publication 2 July 1999)

Si resonant interband tunnel diodes that demonstrate negative differential resistance at room temperature, with peak-to-valley current ratios greater than 2, are presented. The structures were grown using low-temperature (320 °C) molecular-beam epitaxy followed by a postgrowth anneal. After a 650 °C, 1 min rapid thermal anneal, the average peak-to-valley current ratio was 2.05 for a set of seven adjacent diodes. The atomic distribution profiles of the as-grown and annealed structures were obtained by secondary ion mass spectrometry. Based on these measurements, the band structure was modeled and current–voltage trends were predicted. These diodes are compatible with transistor integration. © 1999 American Institute of Physics.

[S0003-6951(99)01935-X]

There is current interest in tunnel diodes, which have characteristics very useful to the circuit designer for applications such as embedded memory and signal processing. Recent review articles<sup>1-3</sup> discuss potential applications of this family of devices in Si. The first tunnel diode, the Esaki diode, 4 which is an intrinsically simple device consisting of a degenerately doped p/n junction, has not found wide use in integrated circuits because of the lack of an epitaxial formation process. Epitaxial processes have been used for Si-based resonant tunnel diodes (RTD), which have demonstrated hole tunneling, 5-10 where the layers are grown on a Si substrate such that the Si barriers are relaxed and the SiGe well layer is compressively strained, and electron tunneling, 11,12 where the barrier layers are relaxed SiGe and the Si well layer is under tensile stress. None of the hole RTDs have reported negative differential resistance (NDR) above a temperature of 77 K, which severely restricts the range of their application. The electron RTD reported by Ismail<sup>11</sup> had a peak-to-valley current ratio (PVCR) of 1.2 at 300 K, while the device reported by Matutinovic-Krstelj<sup>12</sup> only had NDR at temperatures less than 220 K. Additionally, the electron RTDs are not compatible with complimentary metal oxide silicon (CMOS) or heterojunction bipolar transistor (HBT) integration since they require a thick (>1  $\mu$ m) relaxed SiGe buffer layer. A recent device reported by Sardela<sup>13</sup> employing B  $\delta$ -doped layers in Si had NDR at room temperature, with a PVCR of 1.1 and a peak current density of 4.8  $\times 10^3$  A/cm<sup>2</sup>. The exciting feature of the B  $\delta$ -doped device is that the structure is compatible with CMOS and HBT integration, although the PVCR must be increased for the device

to be useful. The search, then, is for a Si-based tunnel diode

which has improved electrical characteristics and which is

interband tunnel diodes (RITD), similar to RITD embodi-

ment originally proposed by Sweeney and Xu.16 By using

low-temperature (370 °C) molecular-beam epitaxy (MBE),

we were able to fabricate Si/Si<sub>0.5</sub>Ge<sub>0.5</sub> RITDs having, at

room temperature, a PVCR of 2.05. By replacing the

Si<sub>0.5</sub>Ge<sub>0.5</sub> with Si, we were able to produce a Si tunnel diode

having a PVCR of 1.41. 15,17 The performance of the tunnel

diodes was found to depend strongly on the  $\delta$ -doping spacing

and on the postgrowth annealing conditions. In this letter, we

will demonstrate Si RITDs which have PVCR values greater

than 2 without the added complexity of Ge.

In our initial study<sup>14,15</sup> we investigated SiGe resonant

compatible with transistor integration.

The Si RITDs were grown on a 75 mm Si (100) B-doped (0.015–0.04  $\Omega$  cm) substrate using solid-source MBE. Prior to entry into the specially designed MBE growth system, <sup>18</sup> the Si substrate was cleaned using a procedure previously described, <sup>19</sup> which resulted in a stable, hydrogen-terminated surface. Si was deposited by e-beam evaporation. The dopants, B and Sb, were obtained by evaporation of elemental

sources in Knudsen cells. The substrate temperature during growth was monitored by an optical pyrometer which was calibrated by observing the eutectic temperatures of Au/Si (363  $^{\circ}$ C) and Al/Si (577  $^{\circ}$ C) on equivalent substrates.

The device structure employed in this study is shown in Fig. 1. The key features of the growth which differentiate this from earlier structures are: (1) lower substrate temperature (320 °C) during growth, which was employed to minimize the segregation of the dopants; (2) increased doping in the  $p^+\delta$  layer; and (3) undoped layers surrounding the

a)Corresponding author. Electronic mail: thompson@estd.nrl.navy.mil

| 30 nm n+ Si           |

|-----------------------|

| 70 nm Undoped Si      |

| Sb Delta-doping Plane |

| 6 nm Undoped Si       |

| B Delta-doping Plane  |

| 20 nm Undoped Si      |

| p+ Si Substrate       |

FIG. 1. Schematic diagram of the nominal Si RITD structure.

δ-doped planes to enhance carrier confinement. Growth was initiated at 650 °C to ensure removal of the hydrogen surface termination. After the growth of 10 nm of undoped Si, the substrate temperature was reduced to 450 °C while an additional 10 nm layer of undoped Si was grown. Si growth was interrupted and, concurrent with the deposition of B (3  $\times 10^{14}$ /cm<sup>2</sup>) in a  $\delta$ -doped layer, the temperature of the substrate was further reduced to 320 °C, which was the final temperature of the substrate during the remainder of the growth. A 6 nm undoped Si spacer layer was grown followed by a second growth interrupt for the deposition of an Sb  $\delta$ -doped layer (3×10<sup>14</sup>/cm<sup>2</sup>). The final layers were a spacer layer of 70 nm of undoped Si followed by 30 nm of Sbdoped ( $>10^{20}/\text{cm}^3$ ) Si for the top Ohmic contact. The Si growth rate was 0.1 nm/s, with the exception of the  $\delta$ -doped regions during which the Si flux was shuttered. Prior to device fabrication, portions of the samples were annealed to determine if postgrowth anneal improved the device characteristics, analogous to our previous RITD work. 14-16 Rapid thermal anneal (RTA) was employed using temperatures of 600, 650, or 700 °C for a period of 1 min.

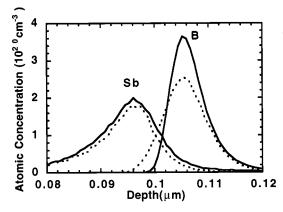

Atomic profiles were obtained by secondary ion mass spectrometry (SIMS) using a high-performance magnetic sector secondary ion mass spectrometer. The net impact energy of the primary beam, 3 keV  ${\rm O_2}^+$ , was selected in order to minimize profile broadening by ion-beam mixing. Depth scales were obtained from stylus profilometry ( $\pm 3\%$  uncertainty). The atomic carrier concentrations of B and Sb were calibrated with implant standards ( $\pm 10\%$  uncertainty). The electrically active portion of the RITD is the region which includes the  $n^+$  layer, the  $p^+$  layer, and the undoped spacer between them. This region is presented in Fig. 2, for the as-grown sample (solid lines) and the sample which under-

FIG. 2. SIMS atomic profiles of the Si RITD, as grown and after a post-growth anneal of 700 °C for 1 min. The region of the device, including the  $\delta$ -doped layers and the intrinsic Si spacer, has been magnified. A linear scale was used to emphasize the effects of the anneal. The as-grown sample is shown with solid lines. The sample annealed at 700 °C is shown with dashed lines.

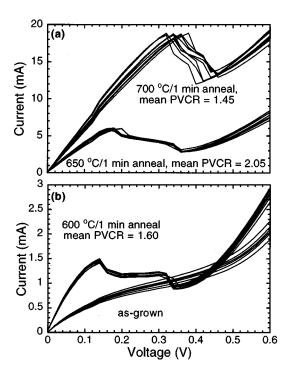

FIG. 3. I-V characteristics for seven adjacent devices after the specified anneal. All measurements are on 18- $\mu$ m-diam diodes and were taken at room temperature. The results are shown on two graphs because of the increased currents after the anneal.

went RTA for 1 min at 700 °C (dashed lines). Some of the width observed in the doping profiles is due to ion-beam mixing during the SIMS measurement. The portion of the dopant profiles extending into the sample are more affected by the SIMS measurement. It is observed that the B  $\delta$ -doped profile was affected by the RTA. The half width at half maximum, toward the surface, increased from 3 to 5 nm. There was a corresponding reduction in the peak B concentration from  $3.6 \times 10^{20}$  to  $2.5 \times 10^{20}$ /cm<sup>3</sup>. The differences observed between the as-grown and annealed Sb  $\delta$ -doped profiles are within the mutual uncertainties of the SIMS measurements. Based on the atomic distributions obtained by SIMS, the band diagrams for the RITD, as-grown, and after RTA for 1 min at 700 °C, were generated by solving the effective-mass Schrödinger equation and corresponding quantum charge for each band and iterating to convergence with Poisson's equation. It was observed that, after anneal, the tunnel region becomes slightly wider due to the B diffusion. The current-voltage (I-V) curves were calculated with a two-band model using the light electron mass of  $0.19 m_0$  and the indirect band gap of 1.12 eV. While the direct tunneling two-band model is not the correct physics for Si, it should predict the correct trends in the magnitude of the current for different junction potentials. These calculations show the current being reduced after RTA, which is consistent with the wider tunnel region, but is inconsistent with the experimental data, as will be shown.

The fabrication process for the RITDs has been previously described. <sup>14</sup> Room-temperature I-V curves were measured from the top of the mesa to the backside Al contact. I-V measurements for seven adjacent devices, having a diameter of 18  $\mu$ m, for the as-grown samples and for each anneal condition, are presented in Fig. 3. It is seen that the as-grown RITDs do not exhibit NDR, but have I-V charac-

teristics of backwards diodes. NDR was observed following a postgrowth RTA between 600 and 700 °C. In the following discussion we focus on four characteristics of these curves: PVCR, the voltage  $V_p$  at which the relative maximum in the current  $I_p$  occurred, and the peak current density  $J_p$ .

The average PVCR was 1.60, 2.05, and 1.45 after a 1 min RTA of 600, 650, and 700 °C, respectively. These roomtemperature values are significantly larger than reported PVCR values for epitaxial Si tunnel diodes at any temperature.  $^{5-14,17}$  It is observed that  $V_p$  shifted to larger values with higher anneal temperature. The plot of  $V_n$  vs  $I_n$ was linear. The intrinsic series resistance obtained from the slope of the curve had a value of 12.2  $\Omega$ . The intrinsic peak voltage of the diodes was obtained from the intercept and had a value of 117 mV. This agreed well with the predicted value of 90 mV from the model. The peak current density increased with the anneal temperature from  $5.7 \times 10^2 \,\mathrm{A/cm^2}$ after the 600 °C/1 min anneal to  $7.3 \times 10^3$  A/cm<sup>2</sup> after the 700 °C/1 min anneal. It is not clear why the device characteristics improved with anneal temperature. The diffusion of the B, observed by SIMS after the 700 °C RTA, widened the tunnel junction by compensating the n-type dopants and should result in a lower peak tunnel current. The simplest explanation for device improvement is the reduction of defects and increased activation of dopants in the quantum wells by the anneal. In the band-structure diagram we assumed complete activation at the growth temperature based on prior work on highly doped thick layers. This assumption may not be valid for the  $\delta$ -doped layers and will be investigated further.

In summary, we have reported on the growth and characterization of Si RITD, which have significantly improved PVCR (>2) compared to previously reported epitaxial Si diodes. The growth was accomplished using low-temperature (320 °C) epitaxy to minimize the segregation of the dopants, which, in turn, permitted a very high concentration of p and n dopants in the quantum wells. A postgrowth RTA between 600 and 700 °C was required to observe NDR. The low

growth and anneal temperatures and the thin epitaxial thickness requirement make these device suitable for CMOS and HBT integration.

This work was supported by the Office of Naval Research, National Science Foundation, and Defense Advance Research Projects Agency. The authors thank Lt. Col. Gernot Pomrenke for his encouragement throughout the project.

- <sup>1</sup>U. Konig, Phys. Scr. **68**, 90 (1996).

- <sup>2</sup>D. J. Paul, Thin Solid Films **321**, 172 (1998).

- A. Seabaugh, X. Deng, T. Blake, B. Brar, T. Broekaert, R. Lake, F. Morris, and G. Frazier, Tech. Dig. Int. Electron Devices Meet. 98, 429 (1998).

L. Esaki, Phys. Rev. 109, 603 (1958).

- <sup>5</sup>H. C. Liu, D. Landheer, M. Buchanan, and D. C. Houghton, Appl. Phys. Lett. **52**, 1809 (1988).

- <sup>6</sup>S. S. Rhee, J. S. Park, R. P. G. Karunasiri, Q. Ye, and K. L. Wang, Appl. Phys. Lett. **53**, 204 (1988).

- <sup>7</sup>E. Kasper, H. Dambkes, and J.-F. Luy, Tech. Dig. Int. Electron Devices Meet. 88, 558 (1988).

- <sup>8</sup>U. Konig, M. Kuisl, J.-F. Luy, and F. Schaffler, Electron. Lett. 25, 1169 (1989).

- <sup>9</sup> U. Gennser, V. P. Kesan, S. S. Iyer, T. J. Bucelot, and E. S. Yang, J. Vac. Sci. Technol. B 8, 210 (1990).

- <sup>10</sup> A. Zaslavsky, D. A. Grutzmacher, Y. H. Lee, W. Ziegler, and T. O. Sedgwick, Appl. Phys. Lett. 61, 2872 (1992).

- <sup>11</sup> K. Ismail, B. S. Myerson, and P. J. Wang, Appl. Phys. Lett. **59**, 973 (1991).

- <sup>12</sup> Z. Matutinovic-Krstelj, C. W. Liu, X. Xiao, and J. C. Sturm, Appl. Phys. Lett. **62**, 603 (1993).

- <sup>13</sup>M. R. Sardela, Jr., H. H. Radamson, and G. V. Hansson, Appl. Phys. Lett. 64, 1711 (1994).

- <sup>14</sup>S. L. Rommel, T. E. Dillon, M. W. Dashiell, H. Feng, J. Kolodzey, P. R. Berger, P. E. Thompson, K. D. Hobart, R. Lake, A. C. Seabaugh, G. Klimeck, and D. Banks, Appl. Phys. Lett. 73, 2191 (1998).

- <sup>15</sup> S. Rommel, T. Dillon, P. Berger, R. Lake, P. E. Thompson, K. D. Hobart, A. C. Seabaugh, and D. S. Simons, Tech. Dig. Int. Electron Devices Meet. 98, 1035 (1998).

- <sup>16</sup>M. Sweeny and J. Xu, Appl. Phys. Lett. **54**, 546 (1989).

- <sup>17</sup> S. L. Rommel, T. E. Dillon, P. Berger, P. E. Thompson, K. D. Hobart, R. Lake, and A. C. Seabaugh, Electron. Device Lett. 20, 329 (1999).

- <sup>18</sup>E. D. Richmond, J. G. Pellegrino, M. E. Twigg, S. Qadri, and M. T. Duffy, Thin Solid Films 192, 287 (1990).

- <sup>19</sup> P. E. Thompson, M. E. Twigg, D. J. Godbey, K. D. Hobart, and D. S. Simons, J. Vac. Sci. Technol. B 11, 1077 (1993).